芯片设计公司为什么要做芯片测试?

1、随着芯片复杂度的提高,内部模块数量不断增加,制造工艺也越来越先进,对应的失效模式变得越来越多,全自动IC测烧代工厂。因此,在设计过程中,芯片设计公司需要更加重视完整有效的芯片测试。

2、设计、制造和测试都可能导致失效。为了确保设计的芯片达到预期目标,制造出的芯片达到要求的良率,以及确保测试的质量和有效性,提供符合产品规范和质量合格的产品给客户,这些都需要在设计的初期就考虑测试方案。3、成本也是一个重要的考量因素。越早发现失效,就能减少不必要的浪费;设计和制造的冗余度越高,全自动IC测烧代工厂,全自动IC测烧代工厂,终产品的良率就越高;同时,获取更多的有意义测试数据可以提供给设计和制造部门,从而有效分析失效模式,改善设计和制造良率。

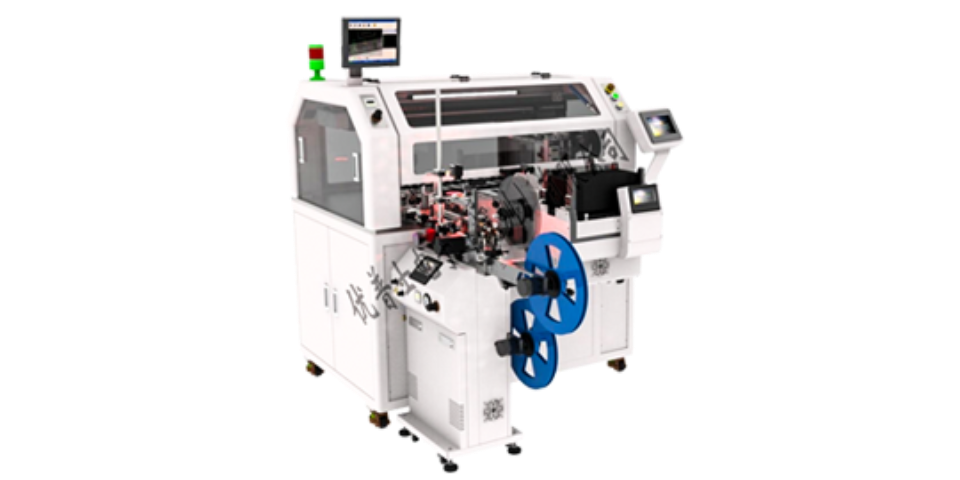

为客户提供好品质,高效率的芯片烧录加工服务。全自动IC测烧代工厂

DIP(DualIn-line Package)双列直插式封装称DIP或DIL(这是欧洲半导体制造商常用的名称)。插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。DIP是普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。引脚中心距2.54mm,引脚数从6到64。封装宽度通常为15.2mm。有的把宽度为7.52mm和10.16mm的封装分别称为skinnyDIP和slimDIP(窄体型DIP)。但多数情况下并不加区分,只简单地统称为DIP。

Cerdip——用玻璃密封的陶瓷双列直插式封装,用于ECLRAM,DSP(数字信号处理器)等电路。引脚中心距2.54mm,引脚数从8到42。在日本,此封装表示为DIP-G(G即玻璃密封的意思)。

DIC——陶瓷DIP(含玻璃密封)的别称DIL——DIP的别称,欧洲半导体厂家多用此名称。

SDIP——收缩型DIP。插装型封装之一,形状与DIP相同,但引脚中心距(1.778mm)小于DIP(2.54mm),因而得此称呼。引脚数从14到90。也有称为SH-DIP的。材料有陶瓷和塑料两种。

SK-DIP——DIP的一种。指宽度为7.62mm、引脚中心距为2.54mm的窄体DIP。通常统称为DIP。

SL-DIP——DIP的一种。指宽度为10.16mm,引脚中心距为2.54mm的窄体DIP。通常统称为DIP。 香洲区高端定制芯片IC测烧经过多年发展,现拥有多项发明专利和丰富的烧录测试资源。

IC产品可靠性等级测试有哪几种?

1、TCT:高低温循环试验(TemperatureCyclingTest)

目的:评估IC产品中具有不同热膨胀系数的金属之间的界面的接触良率。方法是通过循环流动的空气从高温到低温重复变化。

测试条件:

ConditionB:-55℃to125℃

ConditionC:-65℃to150℃

失效机制:电介质的断裂,导体和绝缘体的断裂,不同界面的分层

2、TST:高低温冲击试验(ThermalShockTest)

目的:评估IC产品中具有不同热膨胀系数的金属之间的界面的接触良率。

方法是通过循环流动的液体从高温到低温重复变化。

测试条件:

ConditionB:-55℃to125℃

ConditionC:-65℃to150℃

失效机制:电介质的断裂,材料的老化(如bondwires),导体机械变形

3、HTST:高温储存试验(HighTemperatureStorageLifeTest)

目的:评估IC产品在实际使用之前在高温条件下保持几年不工作条件下的生命时间。

测试条件:150℃

失效机制:化学和扩散效应,Au-Al共金效应

4、可焊性试验(SolderabilityTest)

目的:评估ICleads在粘锡过程中的可靠度测试

方法:Step1:蒸汽老化8小时Step2:浸入245℃锡盆中5秒失效标准(FailureCriterion):至少95%良率

cp测试和ft测试的区别

1)因为封装本身可能影响芯片的良率和特性,所以芯片所有可测测试项目都是必须在FT阶段测试一遍的,而CP阶段则是可选。

2)CP阶段原则上只测一些基本的DC,低速数字电路的功能,以及其它一些容易测试或者必须测试的项目。凡是在FT阶段可以测试,在CP阶段难于测试的项目,能不测就尽量不测。一些类似ADC的测试,在CP阶段可以只给几个DC电平,确认ADC能够基本工作。在FT阶段再确认具体的SNR/THD等指标。

3)由于CP阶段的测试精度往往不够准确,可以适当放宽测试判断标准,只做初步筛选。精细严格的测试放到FT阶段。

4)如果封装成本不大,且芯片本身良率已经比较高。可以考虑不做CP测试,或者CP阶段只做抽样测试,监督工艺。

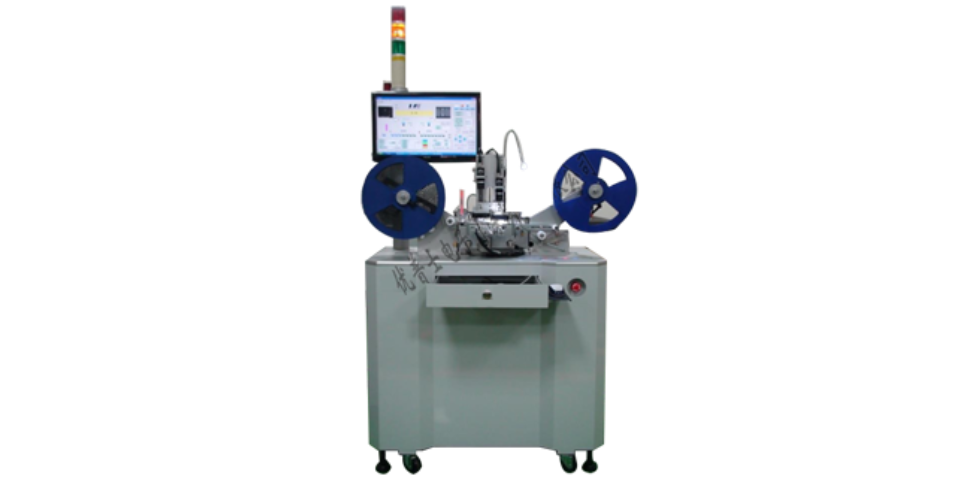

5)新的产品导入量产,应该先完成FT测试程序的开发核导入。在产品量产初期,FT远远比CP重要。等产品逐渐上量以后,可以再根据FT的实际情况,制定和开发CP测试。了解了它们之间的不同,我们还可以根据测试项目的不同和重复内容等因素,在具体测试项目中进行判断和取舍了。毕竟增加一个复杂的高速或高精度模拟测试,不仅会增加治具的成本,还会增加测试机台的费率和延长测试时间,影响出产成果。 OPS用芯的服务赢得了众多企业的信赖和好评。

IC测试座的保养:

1、将芯片清理干净后再放入IC测试座,避免松香、锡渣等杂质进入适配器内污染测试针而造成短路或是接触不良。

2、多次使用之后或者定期对IC测试座进行清洗,可用超声波或是酒精进行清洗。

3、黑色塑胶本体的测试座材料为PEI,易被强力清洁济如天那水、苯、或者稀释剂等腐蚀。请用酒精等中性溶液清洗。使用完后密封存放,以免灰尘或杂质进入测试座内部。

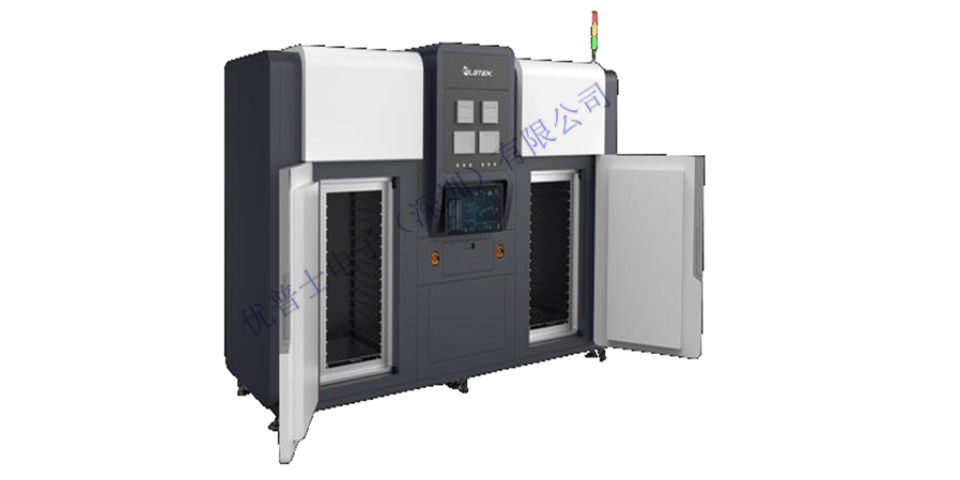

定期的保养,能降低测试的不良率,也能够让IC测试座的寿命更长。 OPS用芯的服务以其专业性、创新性和共赢性,赢得了广大企业的好评和信赖。江门IC测烧代工厂

在芯片生产和使用过程中,优普士提供令客户满意的测试服务,以确保芯片的质量和性能符合要求。全自动IC测烧代工厂

小外形封装是一种很常见的元器件封装形式。表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L字形)。材料有塑料和陶瓷两种。另外也叫SOL和DFP。SOP除了用于存储器LSI外,主要用于规模不太大的ASSP等电路。在输入输出端子不超过10~40的领域,SOP是普及很广的表面贴装封装。引脚中心距1.27mm,引脚数从8~44。另外,引脚中心距小于1.27mm的SOP也称为SSOP;装配高度不到1.27mm的SOP也称为TSOP。还有一种带有散热片的SOP。

SOP封装的应用范围很广,而且以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等在集成电路中都起到了举足轻重的作用。像主板的频率发生器就是采用的SOP封装。

引脚中心距小于1.27mm的SSOP(缩小型SOP);

装配高度不到1.27mm的TSOP(薄小外形封装);

VSOP(甚小外形封装);TSSOP(薄的缩小型SOP);

SOT(小外形晶体管);带有散热片的SOP称为HSOP;

部分半导体厂家把无散热片的SOP称为SONF(SmallOut-LineNon-Fin);

部分厂家把宽体SOP称为SOW(SmallOutlinePackage(Wide-Jype))

全自动IC测烧代工厂

文章来源地址: http://dzyqj.chanpin818.com/jcdl(ic)/danpianji/deta_19335633.html

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

[VIP第1年] 指数:3

[VIP第1年] 指数:3