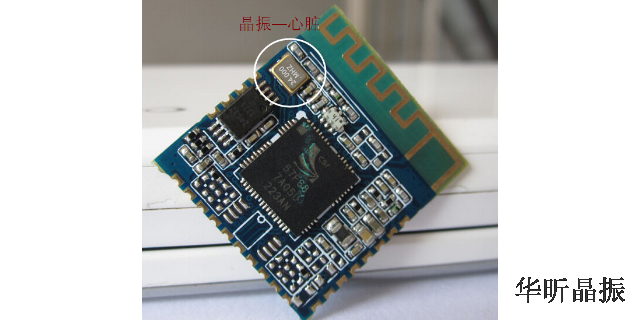

进行晶振的选型以满足特定应用需求时,可以按照以下步骤进行:明确应用需求:首先,需要明确应用的具体需求,包括所需的频率范围、精度、稳定性、温度范围、功耗等。了解晶振类型:了解不同类型的晶振,如有源晶振和无源晶振,以及它们的特点和适用场景。有源晶振通常具有更高的频率稳定性,而无源晶振则更适用于一些简单的应用。确定频率和精度:根据应用需求,选择合适的频率范围和精度。频率范围应满足应用需求,而精度则决定了系统的时序和通信的可靠性。考虑稳定性:对于需要高精度和稳定性的应用,应选择具有较低频率稳定度的晶振,如VCXO或TCXO等。考虑工作环境:根据应用的工作温度范围,选择合适的晶振。同时,还需要考虑晶振的抗冲击能力和抗振动能力。确定封装形式和尺寸:根据系统的布局和安装要求,选择合适的封装形式和尺寸。例如,对于空间受限的应用,可以选择小型封装的晶振。考虑成本和可供应性:在满足应用需求的前提下,考虑晶振的成本和可供应性。尽量选择性价比高、易于采购的晶振。通过以上步骤,您可以进行晶振的选型以满足特定应用需求。晶振的型号含义,晶振型号大全。32MHZ晶振用途

晶振的并联电阻和串联电阻在电路中起着不同的作用,对电路有不同的影响。首先,并联电阻(也被称为反馈电阻)的主要作用是使反相器在振荡初始时处于线性工作区。这有助于稳定无源晶振的输出波形。例如,MHz晶振建议并联1M欧姆的电阻,而KHz晶振则建议并联10M欧姆的电阻。此外,并联电阻还可以提高晶振的抗干扰能力,防止晶振受到外界电磁干扰。其次,串联电阻则主要用于预防晶振被过分驱动。当无源晶振输出波形出现削峰或畸变时,可能意味着晶振存在过驱现象。此时,增加串联电阻可以限制振荡幅度,防止反向器输出对晶振过驱动而将其损坏。串联电阻与匹配电容组成网络,可以提供180度相移,同时起到限流的作用。串联电阻的阻值一般在几十欧姆,具体阻值应根据晶振本身电阻及过驱程度来确定。一般来说,串联电阻的值越小,振荡器启动得越快。总的来说,晶振的并联电阻和串联电阻在电路中各自发挥着关键的作用,通过调整这些电阻的阻值,可以优化晶振的性能,确保电路的稳定性和可靠性。晶振jitter晶振的谐振频率是如何确定的?

晶振的成本与其性能之间存在着密切的关系。首先,晶振的性能,如频率稳定性、老化率、输出信号质量、温度范围以及精度等,都直接影响其成本。高性能的晶振通常具有更高的精度、更低的误差、更宽的温度范围以及更稳定的频率输出,这些都需要在制造过程中采用更先进的技术和材料,从而增加了成本。其次,晶振的材料成本也是决定其总成本的重要因素。晶振的关键部件是晶片,其材料、尺寸和品质都会影响晶振的价格。高质量、高精度的晶片往往价格更高。此外,外壳、引脚等其他材料也会对晶振的成本产生一定的影响。再次,晶振的制造成本也会影响其总成本。制造过程包括切割、研磨、镀膜、封装等环节,这些环节的工艺水平和生产效率都会影响晶振的制造成本。同时,品质控制和测试环节也是制造过程中的重要部分,对于保证晶振的品质和性能也至关重要,而这些环节同样需要投入成本。综上所述,晶振的成本与其性能密切相关。高性能的晶振需要更高的制造成本和更严格的质量控制,因此价格相对较高。而低成本的晶振则可能在性能上有所妥协。

晶振的温漂对电路的影响主要体现在以下几个方面:频率稳定性:晶振是电子设备中的时钟源,为电路提供基准频率。晶振的温漂会导致其输出频率随温度变化,进而影响整个电路的频率稳定性。如果晶振的温漂较大,电路的频率稳定性将受到严重影响,可能导致电路无法正常工作或性能下降。时序控制:电路中的时序控制依赖于晶振提供的基准频率。晶振的温漂会导致时序控制的误差,特别是在需要精确同步的电路中,如通信、数据处理等,这种误差可能导致数据传输错误、信号干扰等问题。功耗和发热:晶振的温漂还可能导致电路功耗的增加和发热问题的加剧。因为为了维持电路的稳定工作,可能需要额外的功耗来补偿晶振温漂带来的影响。同时,晶振本身的发热问题也可能因为温漂而加剧,进一步影响电路的性能和稳定性。为了减小晶振温漂对电路的影响,可以采取一些措施,如使用温度补偿晶振、恒温晶振等,以提高晶振的频率稳定性和降低温漂。此外,在设计电路时,也需要充分考虑晶振的温漂特性,选择合适的晶振型号和规格,并合理布局电路以降低温度对晶振的影响。单片机晶振必要性探讨,单片机晶振常见问题分析。

晶振的相位噪声在频域上被用来定义数据偏移量。对于频率为f0的时钟信号而言,如果信号上不含抖动,那么信号的所有功率应集中在频率点f0处。然而,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,它们分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。相位噪声就是信号在某一特定频率处的功率分量,将这些分量连接成的曲线就是相位噪声曲线。它通常定义为在某一给定偏移处的dBc/Hz值,其中dBc是以dB为单位的该功率处功率与总功率的比值。例如,一个振荡器在某一偏移频率处的相位噪声可以定义为在该频率处1Hz带宽内的信号功率与信号总功率的比值。相位噪声对电路的影响主要体现在以下几个方面:频率稳定性:相位噪声的增加会导致振荡器的频率稳定性下降,进而影响整个电路的工作稳定性。通信质量:在通信系统中,相位噪声会影响信号的传输质量,增加误码率,降低通信的可靠性。系统性能:相位噪声还会影响电路的其他性能指标,如信噪比、动态范围等,进而影响整个系统的性能。因此,在电路设计中,需要采取一系列措施来降低晶振的相位噪声,以保证电路的稳定性和性能。例如,可以选择低噪声的晶振、优化电路布局、降低电源电压波动等。什么是晶振的Q值?它如何影响电路性能?16m无源晶振

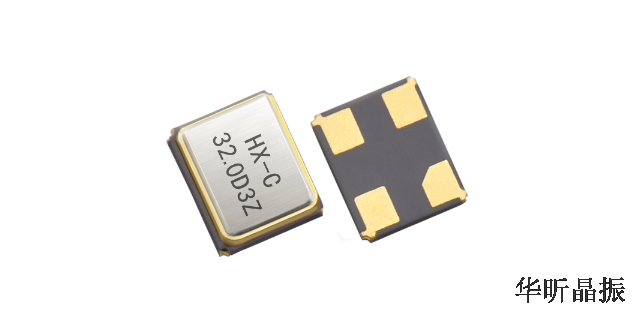

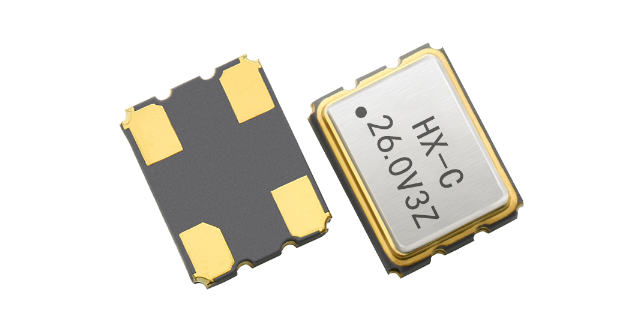

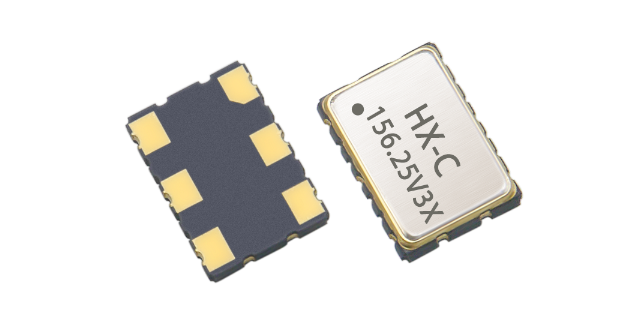

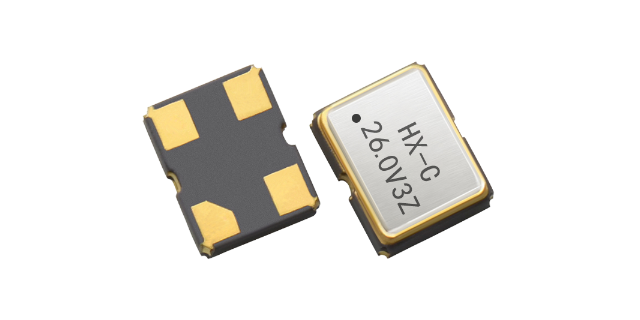

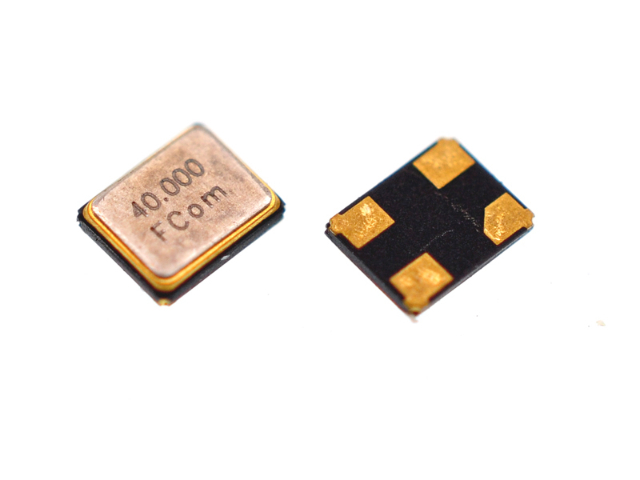

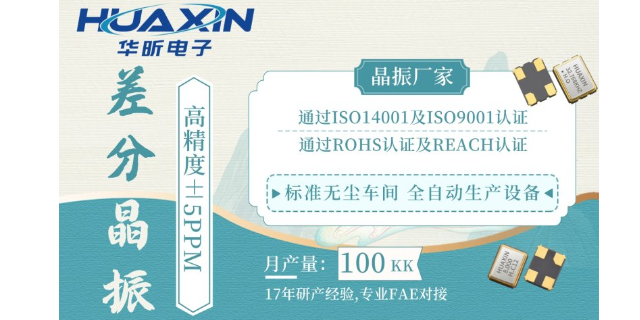

晶振型号齐全,全品类。32MHZ晶振用途

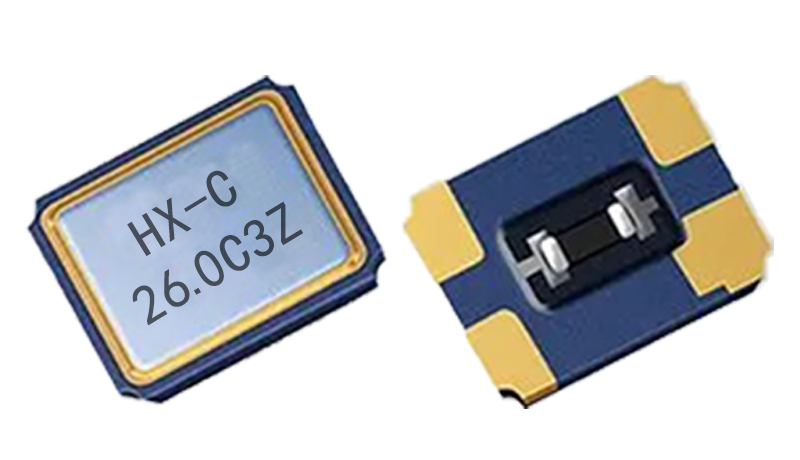

提高晶振的精度和稳定性主要可以从以下几个方面着手:优化制造工艺:通过改进制造过程中的切割、清洗、镀膜等步骤,减少制造公差,提高晶振的精度。采用高质量晶片:选择品质优良的石英晶片作为原材料,确保晶振具有更好的物理性能和稳定性。采用先进的封装技术:选择适当的封装材料和封装方式,以减少外部环境对晶振的影响,提高稳定性。同时,一些封装技术还设计了温度补偿机制,能够进一步提高晶振的精度。优化电路设计:在晶振的电路设计中,采用线性电源或低噪声电源,加入滤波电容以减少电源噪声。同时,优化PCB布局布线,减小寄生电感电容的影响。外部干扰防护:采取屏蔽措施以减少外部电磁干扰对晶振的影响。例如,使用金属罩来保护晶振,或者采购抗干扰能力更强的差分晶振。精确匹配电容:精细无误的电容匹配能让晶振发挥出更稳定的功效。在选取电容时,要尽可能选用精度高的电容器,并且尽量选用数值一样的电容器,以避免使用误差大的电容器导致晶振频率产生偏差。通过以上措施,可以有效提高晶振的精度和稳定性。32MHZ晶振用途

文章来源地址: http://dzyqj.chanpin818.com/ydjtplyj/deta_22096917.html

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

[VIP第1年] 指数:3

[VIP第1年] 指数:3